## Embedded Systems – Lab 2: **Interrupts and Timers**

Marco Giordano, mgiordano@ethz.ch

Center for Project Based Learning, ETH Zurich

#### **Lab Structure**

#### Topic of today's lab:

Learn how interrupts and timers work in an MCU.

#### Agenda:

16:15 – 16:45 Introduction

16:45 - 18:00Working on LAB tasks

Available Assistants: Filippo, Gabriel, Richard

#### Goal of this lab

- Configuration of hardware interrupts

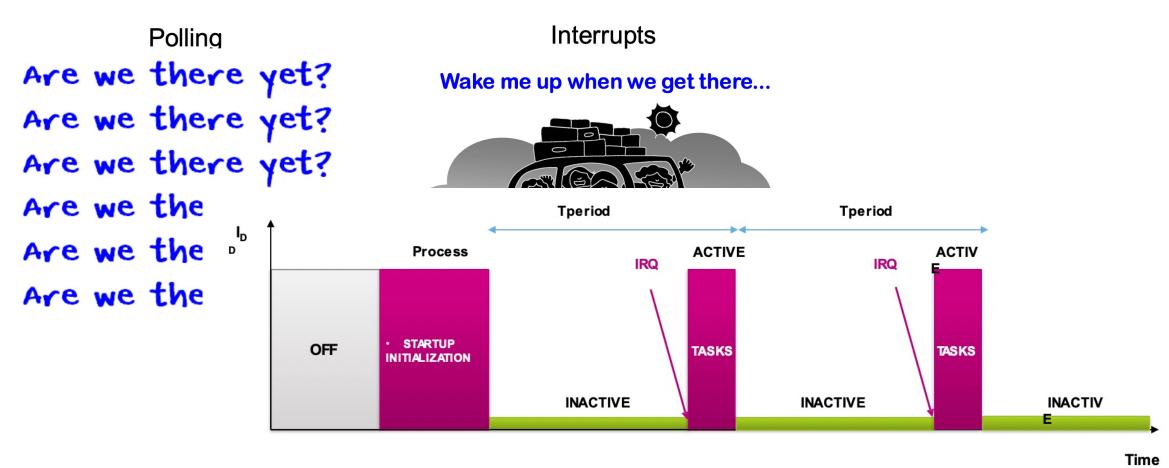

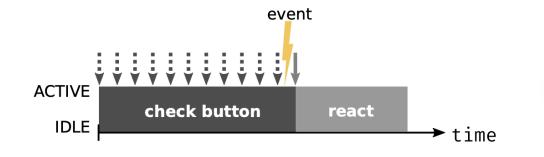

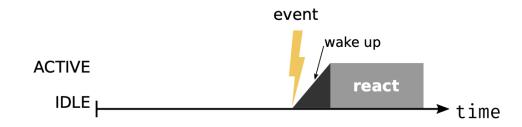

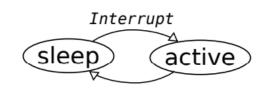

- Interrupt vs. Polling

- Learn how to debug program running on a microprocessor

- Configuration of hardware timers

- Implementation of pulse-width modulation (PWM)

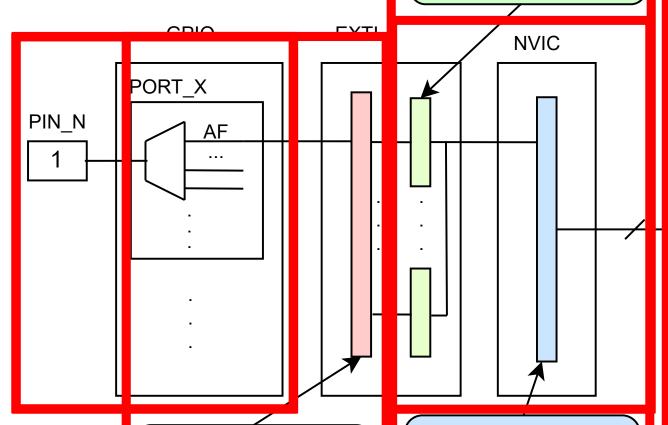

Definition: an hardware interrupt is an electronic signal that alerts the microprocessor of an event. An interrupt can be triggered by either an internal peripheral (e.g. timer) or an external device (e.g. button)

EXTI IMR

Exti Interrupt Mask Register: singularly masks interrupt pins NVIC\_ISER/NVIC\_ICER

EXTI\_RTSR/EXTI\_FTSR

Rising and Falling trigger selection register

**CORE**

0-15: NMI

INTERRUPT

Interrupt Set-Enable and Clear-Enable Registers: to activate single interrupts (also from pheriperals)

Table 153. STM32U575/585 vector table

| 14215 155. 51525010/000 700001 14210 |                |                  |                      |                                                                                          |                              |

|--------------------------------------|----------------|------------------|----------------------|------------------------------------------------------------------------------------------|------------------------------|

| Position                             | Priority       | Type of priority | Acronym              | Description                                                                              | Address                      |

| -                                    | -              | -                | -                    | Reserved                                                                                 | 0x0000 0000                  |

| -                                    | -4             | Fixed            | Reset                | Reset                                                                                    | 0x0000 0004                  |

| -                                    | -2             | Fixed            | NMI                  | Non maskable interrupt. The RCC clock security system (CSS) is linked to the NMI vector. | 0x0000 0008                  |

| -                                    | -3<br>or<br>-1 | Fixed            | Secure HardFault     | Secure hard fault                                                                        | 0x0000 000C                  |

| -                                    | -1             | Fixed            | Non-secure HardFault | Non-secure hard fault. All classes of fault                                              | 0x0000 000C                  |

| -                                    | 0              | Settable         | MemManage            | Memory management                                                                        | 0x0000 0010                  |

| -                                    | 1              | Settable         | BusFault             | Pre-fetch fault, memory access fault                                                     | 0x0000 0014                  |

| -                                    | 2              | Settable         | UsageFault           | Undefined instruction or illegal state                                                   | 0x0000 0018                  |

| -                                    | 3              | Settable         | SecureFault          | Secure fault                                                                             | 0x0000 001C                  |

| -                                    | -              | -                | -                    | Reserved                                                                                 | 0x0000 0020 -<br>0x0000 0028 |

| -                                    | 4              | -                | SVC                  | System service call via SWI instruction                                                  | 0x0000 002C                  |

| -                                    | 5              | -                | Debug Monitor        | Debug monitor                                                                            | 0x0000 0030                  |

| -                                    | -              | -                | -                    | Reserved                                                                                 | 0x0000 0034                  |

| -                                    | 6              | Settable         | PendSV               | Pendable request for system service                                                      | 0x0000 0038                  |

| -                                    | 7              | Settable         | SysTick              | System tick timer                                                                        | 0x0000 003C                  |

| _                                    |                |                  |                      |                                                                                          |                              |

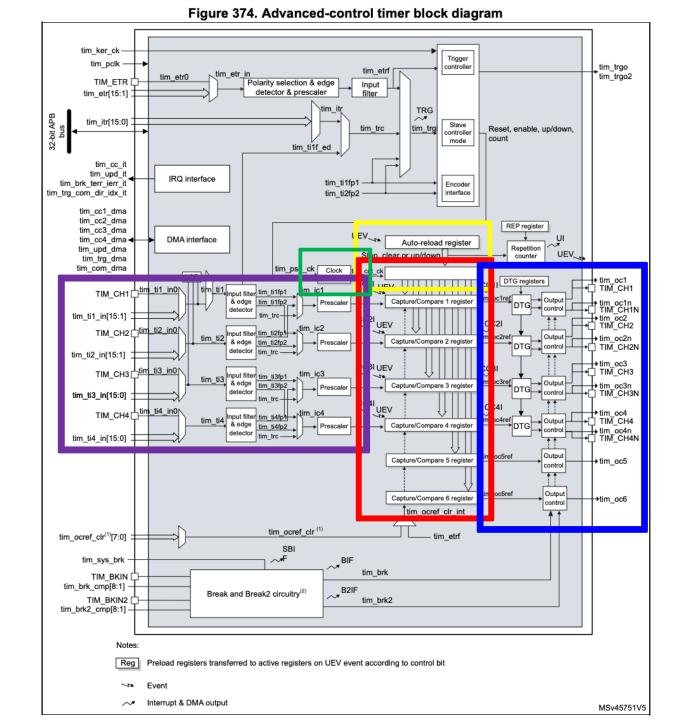

## **Timers**

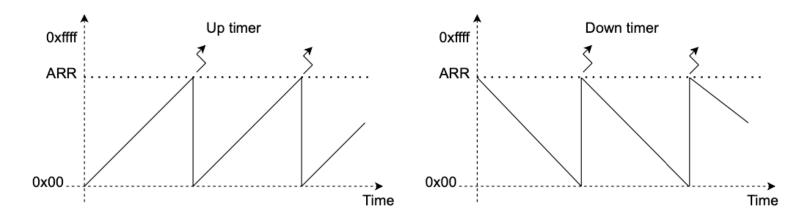

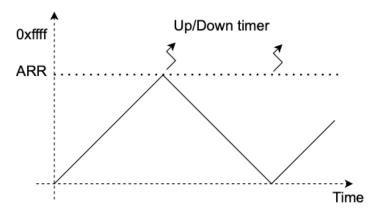

## Timers – Up, Down and Up/Down

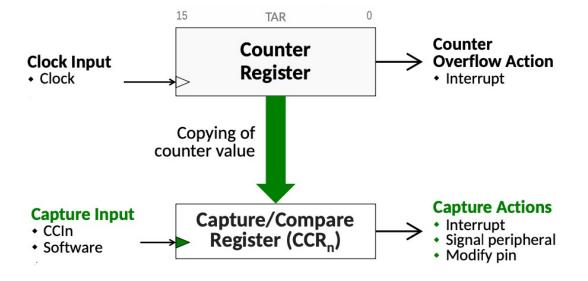

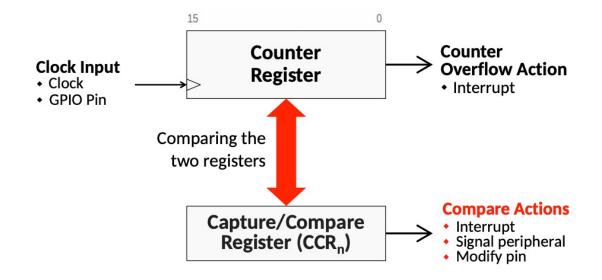

## **Timers – Input Capture and Output Compare**

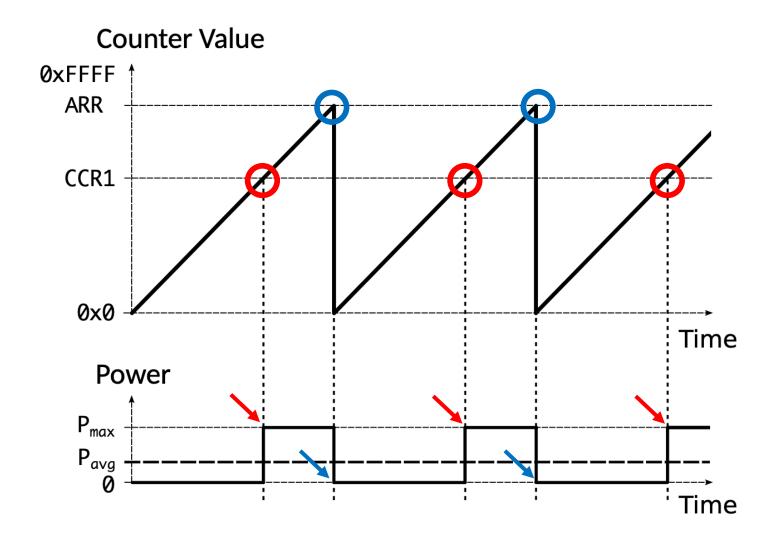

## **Timers - PWM**

### Tasks of Lab 2

- Task 1:

- Interrupts

- Debugging

- Task 2:

- **Timers**

- **PWM**

#### Tasks of Lab 2

- Introduction is over. Feel free to ask questions!

- The assistants are now available until 18:00 to answer questions.

- Email: For individual questions, you can also reach me under <u>mgiordano@ethz.ch</u>.

- On Friday from 16:15 18:00, we will repeat the session.

#### Happy coding!